| spanish.china.org.cn | 11. 10. 2025 | Editor:Teresa Zheng |  |

|

|

|

|

[A A A] |

Avance revolucionario en chips flash 2D

La tecnología integrada puede acelerar los programas de IA

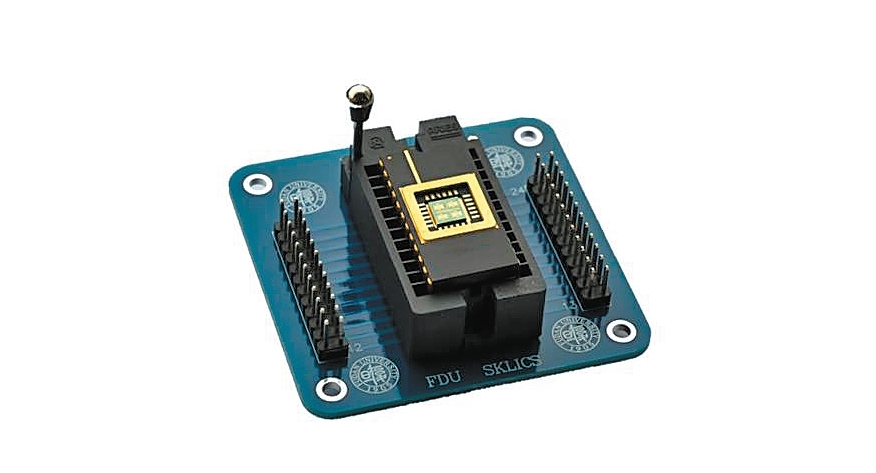

Un equipo de la Universidad de Fudan en Shanghai ha desarrollado el primer chip flash 2D con todas las funciones para la integración de sistemas, lo que supone un hito en la ingeniería de este tipo de dispositivos.

El adelanto combina la memoria flash 2D ultrarrápida con semiconductores complementarios de óxido metálico (CMOS) a partir del silicio para dar con un modelo que acelera la transición de dispositivos disruptivos de próxima generación de la teoría a la práctica y ofrece un sólido apoyo para el paso de la tecnología de la información hacia una nueva era de alta velocidad.

El chip admite operaciones de instrucción de 8 bits, operaciones paralelas de alta velocidad de 32 bits y acceso aleatorio, con un rendimiento de celda de memoria del 94,3 %. Su velocidad supera a la de la actual memoria flash, lo que supone el primer chip flash híbrido de silicio 2D, según los científicos.

El miércoles se publicó un artículo en la revista Nature en el que se detallan los resultados del estudio.

En la era de la inteligencia artificial (IA), la demanda de un acceso más rápido a los datos ha crecido de forma exponencial, mientras que la velocidad y el consumo energético limitados de las memorias tradicionales han devenido trabas para dichos programas.

En abril, el mismo equipo presentó en Nature el prototipo de memoria flash PoX 2D, con una velocidad de programación sin precedentes de 400 picosegundos, la más rápida hasta la fecha.

Sin embargo, el proceso de industrialización de adelantos de primer nivel para aplicaciones de sistema suele llevar mucho tiempo. El equipo del Laboratorio Estatal Clave de Chips y Sistemas Integrados de la Universidad de Fudan y la Facultad de Circuitos Integrados, Microelectrónica y Nanoelectrónica, integró el flash 2D en la plataforma CMOS del sector, brindando una forma de convertir el concepto en una aplicación de sistema complejo.

«Han pasado unos 24 años desde el primer prototipo de transistor semiconductor hasta la primera CPU. Sin embargo, al combinar tecnologías emergentes en la plataforma CMOS existente, el proceso es mucho más corto. Podemos acelerar aún más la exploración de usos disruptivos en el futuro», afirmó Liu Chunsen, responsable del proyecto y uno de los autores del artículo.

Zhou Peng, otro de los autores e investigador principal del equipo, anotó que creían que los dispositivos de almacenamiento probablemente serían los primeros 2D en industrializarse, debido a sus modestas exigencias en la calidad de los materiales y los procesos de fabricación, así como sus métricas de rendimiento que superan con creces las tecnologías actuales.

Los científicos explicaron que los chips actuales llevan en su mayoría silicio. Estos componentes con los de los 2D son muy diferentes, ya que las obleas de silicio suelen tener un grosor de cientos de micrómetros, mientras que las de semiconductores 2D poseen un grosor atómico de menos de 1 nanómetro.

Uno de los principales retos era cómo unir los materiales 2D con la tecnología CMOS sin comprometer el rendimiento. La superficie de un circuito CMOS es bastante rugosa debido a sus elementos subyacentes, mientras que los de los semiconductores 2D solo tienen un espesor de 1 a 3 átomos. Estos materiales pueden romperse fácilmente si se colocan directamente sobre circuitos CMOS.

«Es como ver Shanghai desde el espacio. Parece plana, pero dentro de la ciudad hay edificios de diferentes alturas: más de 400 metros, 100 metros o solo unas docenas de metros. Si se coloca una lamina delgada sobre la ciudad, la misma en sí no sería plana», precisó Zhou, y añadió que esto explica por qué los investigadores de semiconductores 2D de todo el mundo solo pueden procesar materiales sobre sustratos nativos extremadamente planos hasta ahora.

En su estudio, el equipo decidió comenzar con materiales 2D con un cierto grado de flexibilidad. Mediante una integración modular, fabricó los circuitos de memoria 2D en los circuitos CMOS maduros y utilizó la interconexión monolítica de alta densidad para la comunicación entre los distintos módulos. Esta innovadora técnica permite el acoplamiento estrecho de componentes 2D con sustratos CMOS a escala atómica.

El grupo sostuvo que el chip ha completado con éxito el proceso de tape-out. Para el siguiente paso, se tiene previsto una línea de producción piloto y la colaboración con instituciones afines para crear un proyecto de ingeniería para una escala de megabytes en 3 a 5 años.

Los expertos indicaron que el estancamiento actual de los sistemas de IA pasa de la potencia de cálculo front-end al almacenamiento y los datos back-end, y que los modelos a futuro serán cada vez más grandes. Algunos especialistas del rubro mostraron optimismo y dijeron que este logro irá del laboratorio a las aplicaciones a gran escala a un ritmo más célere, en escenarios como computadoras personales y dispositivos móviles.

«Este estudio representa una "tecnología fuente" en el campo de los circuitos integrados de China, lo que permite al país tomar la delantera en tecnologías de almacenamiento central de punta», destacó Zhou.